HOME > PRODUCT

Product introduction

Product introduction

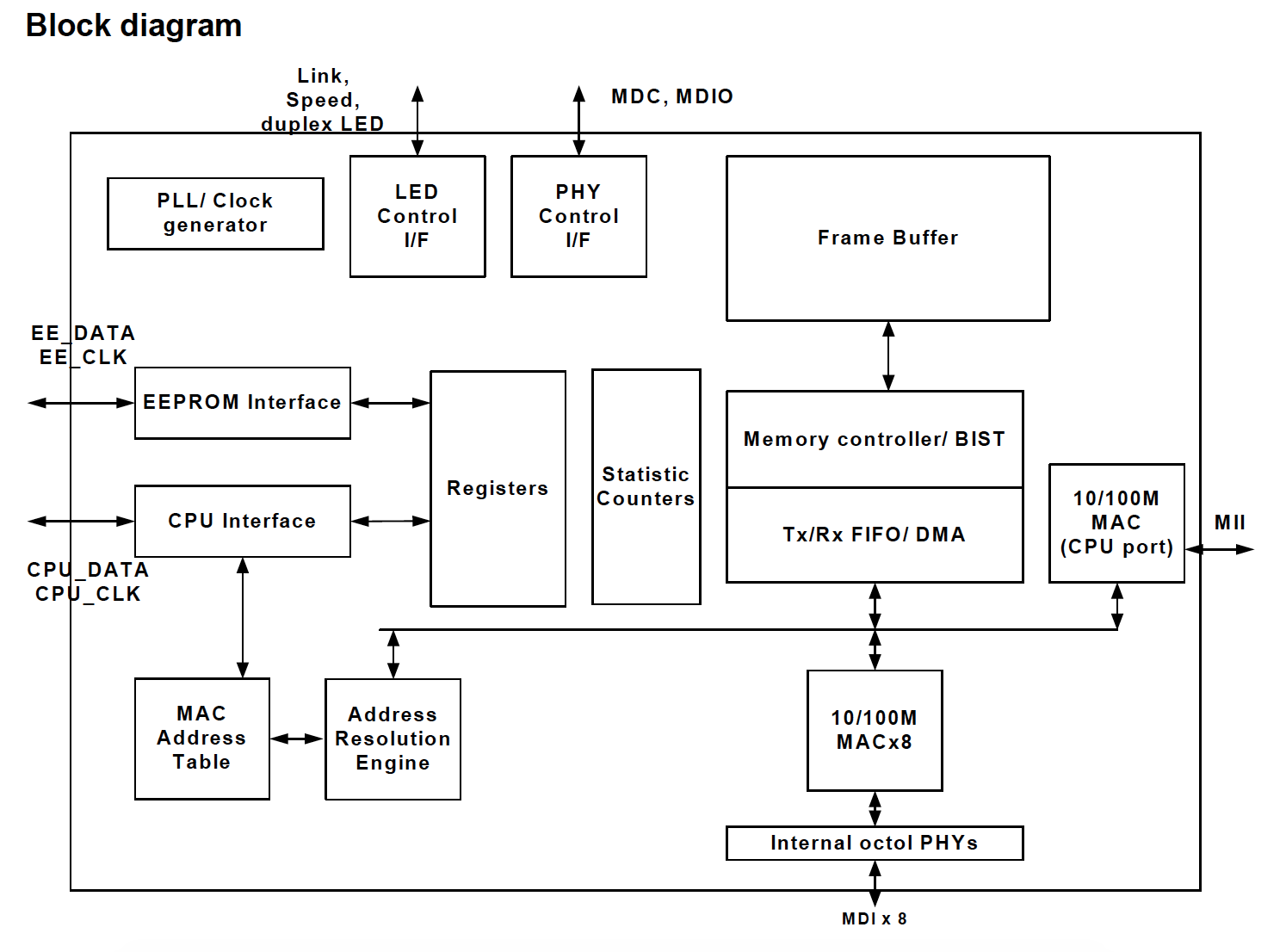

- IP179L

- 8+1 ports Ethernet Switch Controller with Octal-PHYs

Features

Built in 8 internal PHY, and one MII

1.25Mbits packet buffer memory

Support packet length up to 1600 Bytes

Store & forward, share memory, non-blocking architecture

Support flow control

802.3x in full duplex

Collision / Carrier sense based backpressure in half duplex

Provide up to 4K MAC address entries

CRC/ direct hashing algorithm

Programmable aging timer (55s~1812070.4s)

Wire speed address learning and resolution

CPU accessible for security and static MAC

Learning enable/disable

Support Sniffer function (in, out, in & out)

Support IGMP snooping function Version 1,2

Support up to 2 trunk group

Support up to 2 trunk groups

(Port0~3, port4~7)

Load balance based on (port, DA, SA, DA / SA)

Support VLAN(20 VLAN groups)

Port based VLAN

Tag based VLAN based on Ports & VIDs

Add/ remove/ modify tag

Support Class of Service

Port based COS function

802.1Q priority tag based

IP TOS based (IPv4/IPv6)

TCP/UDP port based

4 queues for per port

WRR/ FIFS/ SP algorithm

Broadcast storm control support

Broadcast rate control per port

Block broadcast packet that not belongs to ARP or IPv4 packet to CPU port

Support port security

MAC address based

TCP/UDP port based

Supports Bandwidth control- 255 configurable levels for P0-P8, (from 32kbps to 7.96 Mbps) for low bandwidth

255 configurable levels for P0-P8 (from 512kbps to 100 Mbps) for high bandwidth

With/without flow control

Support SMI auto-polling function

Poll for speed, duplex, flow control, and link

Support Reverse MII 100M full duplex only

CPU accessible (interrupt support)

CPU R/W PHY registers

Support 4 port states for Spanning Tree protocol

Discarding/Blocking/learning/ forwarding

Forward BPDU to CPU port

Captures specific packet to CPU port

BPDU, LACP, 802.1X, GMRP, GVRP, ARP

ICMP, IGMP, TCP, UDP, OSPF, other IP protocols

Packets with specific TCP/UDP port number

Flexible PHY address setting for CPU.

Support three Configuration modes

Pin initial setting

2 wire serial interface for EEPROM

2 wire serial interface for CPU

Statistic counters for each port

RX/TX packet count

CRC error packet count

Drop packet count

Collision count

Support Non association port

Support port based address flush

Support LED functions (for p0~p7)

Support 2 bit serial,3 bit serial, and 3 bit bi color mode

Support direct LED mode for Link/Activity, speed, duplex states

Support bi color direct LED mode

Only one 25MHz crystal is needed

Adjustable IO voltage (3.3v MII)

Programmable MAC address table through CPU interface

128 pin LQFP EPAD package

Built in 8 internal PHY, and one MII

1.25Mbits packet buffer memory

Support packet length up to 1600 Bytes

Store & forward, share memory, non-blocking architecture

Support flow control

802.3x in full duplex

Collision / Carrier sense based backpressure in half duplex

Provide up to 4K MAC address entries

CRC/ direct hashing algorithm

Programmable aging timer (55s~1812070.4s)

Wire speed address learning and resolution

CPU accessible for security and static MAC

Learning enable/disable

Support Sniffer function (in, out, in & out)

Support IGMP snooping function Version 1,2

Support up to 2 trunk group

Support up to 2 trunk groups

(Port0~3, port4~7)

Load balance based on (port, DA, SA, DA / SA)

Support VLAN(20 VLAN groups)

Port based VLAN

Tag based VLAN based on Ports & VIDs

Add/ remove/ modify tag

Support Class of Service

Port based COS function

802.1Q priority tag based

IP TOS based (IPv4/IPv6)

TCP/UDP port based

4 queues for per port

WRR/ FIFS/ SP algorithm

Broadcast storm control support

Broadcast rate control per port

Block broadcast packet that not belongs to ARP or IPv4 packet to CPU port

Support port security

MAC address based

TCP/UDP port based

Supports Bandwidth control- 255 configurable levels for P0-P8, (from 32kbps to 7.96 Mbps) for low bandwidth

255 configurable levels for P0-P8 (from 512kbps to 100 Mbps) for high bandwidth

With/without flow control

Support SMI auto-polling function

Poll for speed, duplex, flow control, and link

Support Reverse MII 100M full duplex only

CPU accessible (interrupt support)

CPU R/W PHY registers

Support 4 port states for Spanning Tree protocol

Discarding/Blocking/learning/ forwarding

Forward BPDU to CPU port

Captures specific packet to CPU port

BPDU, LACP, 802.1X, GMRP, GVRP, ARP

ICMP, IGMP, TCP, UDP, OSPF, other IP protocols

Packets with specific TCP/UDP port number

Flexible PHY address setting for CPU.

Support three Configuration modes

Pin initial setting

2 wire serial interface for EEPROM

2 wire serial interface for CPU

Statistic counters for each port

RX/TX packet count

CRC error packet count

Drop packet count

Collision count

Support Non association port

Support port based address flush

Support LED functions (for p0~p7)

Support 2 bit serial,3 bit serial, and 3 bit bi color mode

Support direct LED mode for Link/Activity, speed, duplex states

Support bi color direct LED mode

Only one 25MHz crystal is needed

Adjustable IO voltage (3.3v MII)

Programmable MAC address table through CPU interface

128 pin LQFP EPAD package

Technical reference

Technical reference

Data download

Warning: Invalid argument supplied for foreach() in /www/wwwroot/cybertop.com.cn/en/product_detail.php on line 93